#### **Overview**

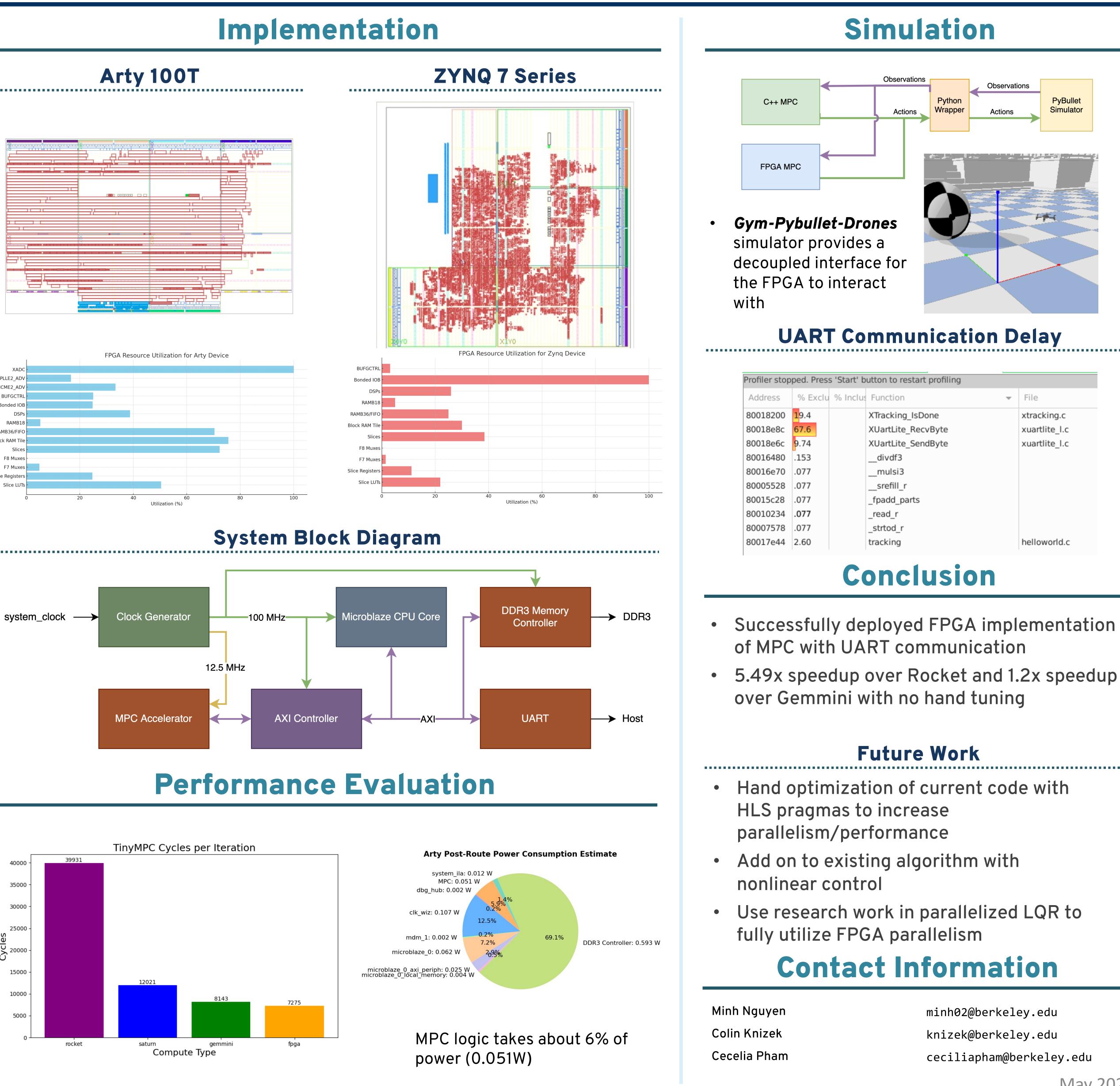

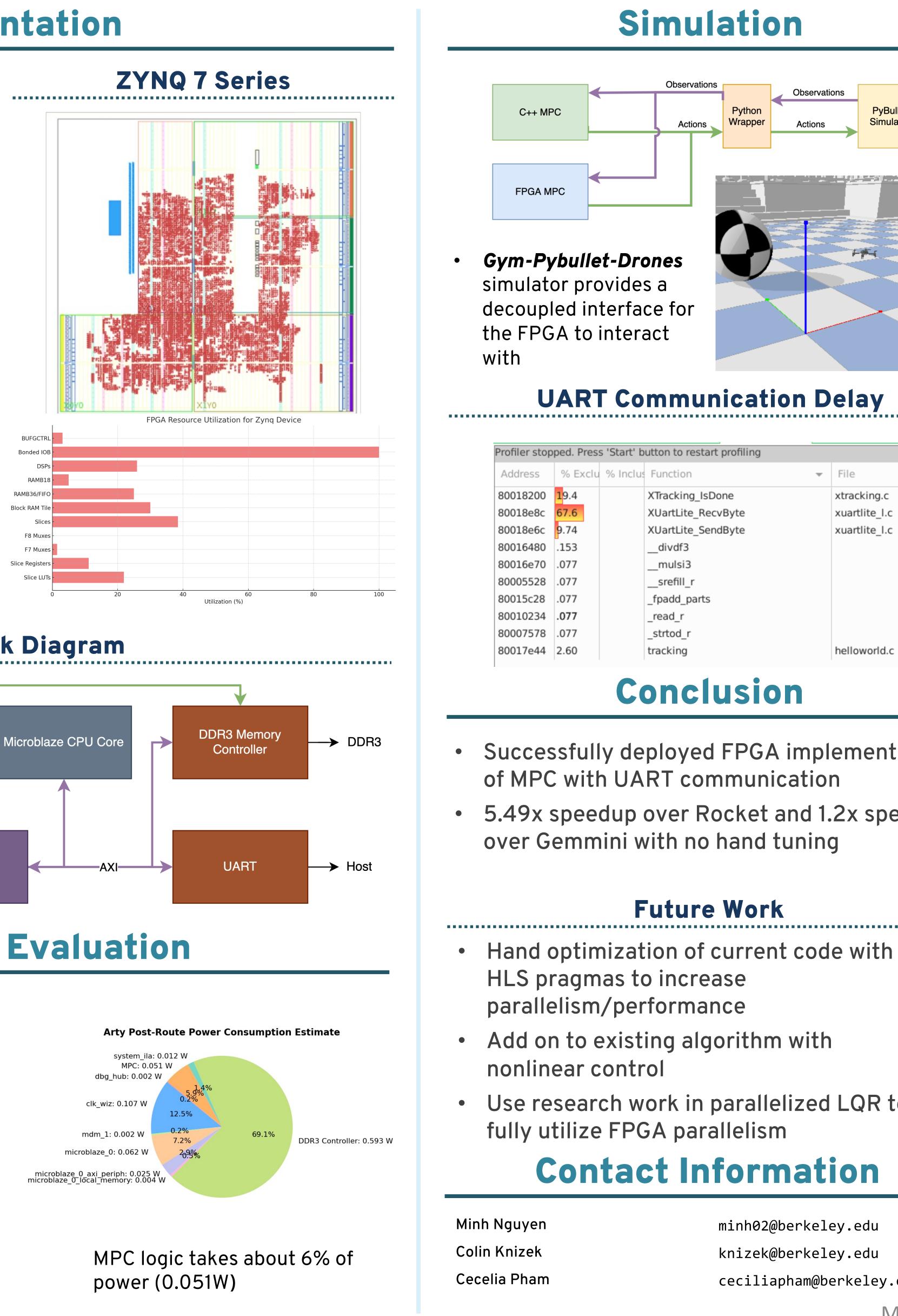

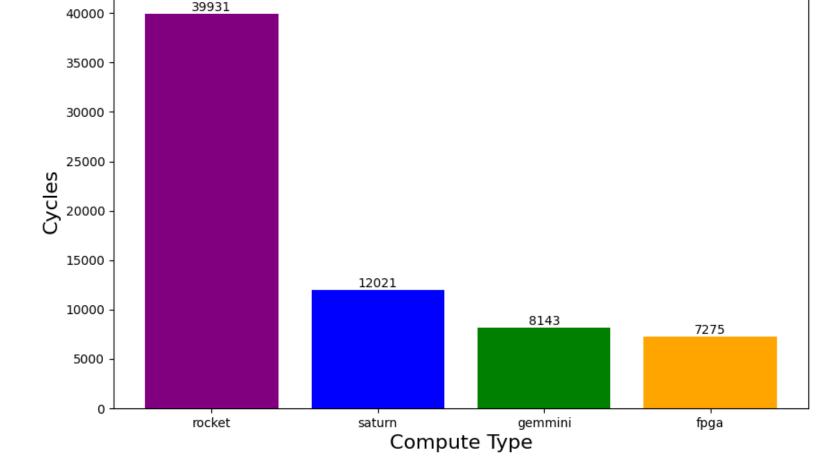

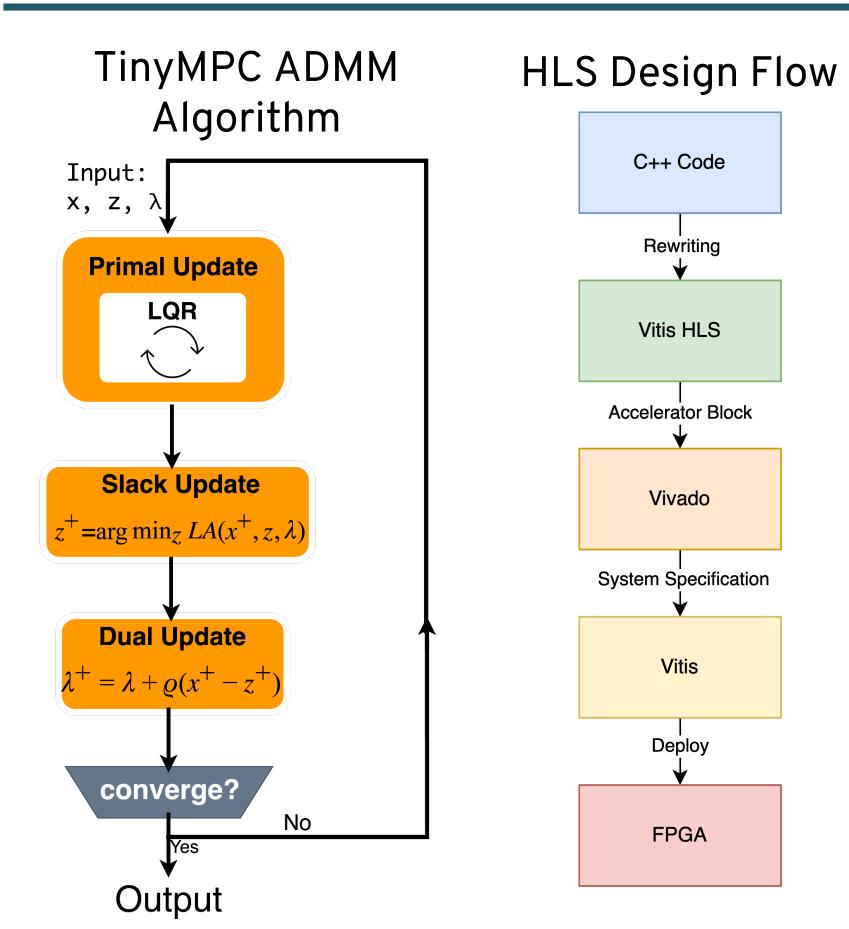

We took an existing MPC algorithm (TinyMPC) and adapted it to HDL using High Level Synthesis (HLS). We then deployed the algorithm on two common FPGAs and tested the performance on a simulated end to end workload

# Motivation

- Resource constrained robotic platforms have difficulty running online control algorithms

- FPGAs offer high performance and flexibility but are difficult to program

## Background

- MPC is a control algorithm that uses a  $\bullet$ robot's dynamics to calculate an optimal trajectory

- MPC is computationally intensive so  $\bullet$ want to use custom hardware for speedups

- HLS turns C code to Verilog with  $\bullet$ appropriate pipelining and parallelism

- Use HLS to take annotated MPC code  $\bullet$ and turns it into an accelerator block to be incorporated into an SOC

PLLE2\_ADV BUFGCTRL Bonded IOB RAMB18 RAMB36/FIFO Block RAM Tile F8 Muxes F7 Muxes Slice Registe

Slice LUTs

## **FPGA Implementation of Model Predictive Control** using High Level Synthesis

Minh Nguyen, Colin Knizek, Cecelia Pham